# To Design a Pulse Generator for the Solar Power Multi Level Inverter in Over-Modulation Mode

Bharat Modi<sup>1</sup>, Dinesh Kumar<sup>2</sup>, Shubhi Jain<sup>3</sup>, Mohit Kumar Sharma<sup>2</sup>, Garvit Gupta<sup>1</sup>, Jinendra Rahul<sup>1</sup>

<sup>1</sup>Department of Electrical Engineering, Swami Keshvanand Institute of Technology Management & Gramothan jaipur, India bharat.modi@skit.ac.in, jinendra.rahul@skit.ac.in,garvit.gupta@skit.ac.in

<sup>2</sup>VGU, Department of Electronics and Communication Engineering, Jaipur, India

dverma646@gmail.com, mohit.kumar.sharma@vgu.ac.in

<sup>3</sup>SKIT, Department of Electronics and Communication Engineering, Swami Keshvanand Institute of Technology Management &

Gramothan jaipur, India

shubhi.jain@skit.ac.in

Received: 05 Mar 2024; Received in revised form: 06 Apr 2024; Accepted: 12 Apr 2024; Available online: 18 Apr 2024 ©2024 The Author(s). Published by AI Publications. This is an open access article under the CC BY license (https://creativecommons.org/licenses/by/4.0/)

Abstract— Over modulation (OM) phenomenon has been investigated through several Pulse Width Modulation (PWM) techniques in the Solar Power Multi Level Inverter. However, due to non-linear characteristics and a severe low harmonics ripple, it has not been used in closed-loop control with small power grid connected solar panel however it is beneficial to work in over modulation region to utilize the maximum DC bus voltage in open loop system.

Keywords— Pulse Width Modulation, Over-Modulation, Modulation-index.

# I. INTRODUCTION

Over-modulation produces a lot of distortion in the current because the average voltage of the pole is not a sinusoidal signal. The common mode voltage is removed due to Over-modulation and only pure sinusoidal wave appears in the output. It can increase the voltage by up to 15% more than the voltage of the line. It is also possible to reduce the switching losses. We can get 0.644  $V_{dc}$  by implementing this. It is adopted to increase the use of the DC Bus. It can also generate higher AC side voltage (at the same DC bus voltage). However, the only issue with over-modulation is that it induces low harmonic distortion in the output, thus low frequency current appears which causes many problems in the control of the closed loop [1].

Proposed different methods of neutral point clamped inverters and concluded that the idea of multilevel inverters has been picking up prevalence in the ongoing years fundamentally because of improved control quality, decreased device stress, the better similarity of electromagnetic and higher capacity of the output voltage [2]. The escalier patterned output voltage allows a decrease in total harmonic distortion (THD), it also lowers the dv/dt and this is how it requests low switching frequency to oversee the switching harmonic spectrum to lower the switching losses [3]. The space vector graph of any threephase n-level inverter comprises six sectors. Every sector comprises (n -1)2 triangles. Every vertex of the triangle represents a switching vector. A switching vector represents at least one switching state relying upon its location. There are n3 switching states in the space vector graph of an n-level inverter. Every SVPWM method has their different switching states according to their respective space vector triangle and this is done by choosing correct switching states foe different on-times. Introduced a control strategy which lessens the distortion in output waveform hence, harmonics reduces and by using this strategy it can perform the buck-boost operation too [4]. Suggested PWM methods for multilevel inverters and deduced that the main advantage of using multi-level inverter (MLI) is that it reduces the common-mode voltage (CMV) when applied in drive applications. Other than that, to introduce the issue of CMV for MLI, the

researchers suggested an array of modulation procedures [5, 6].

#### II. OVER-MODULATION

Among the various reasons, one of the most important reasons is to increase the DC bus utilization. Now with sine triangle PWM the maximum fundamental voltage whatever we could get was (fundamental voltage $0.5V_{dc}$  after adding third harmonic injection we can get $0.577V_{dc}$  i.e. 15% more) but in over-modulation, we can get maximum 6 step voltage i.e. $0.644V_{dc}$  of fundamental voltage. But there is a problem; it introduces low-frequency distortion in the output. If the supply is balanced than,

$$V_{RN} + V_{YN} + V_{BN} = 0 (1)$$

$$V_{\rm c} = \frac{3}{2} V_{RN} \tag{2}$$

$$V_{\beta} = \frac{\sqrt{3}}{2} (V_{RN} - V_{BN})$$

(3)

Equation no 1, 2 & 3 are used to convert 3 phase into the 2 phase voltages and the orthogonal components of the voltage space vector or the average voltage vector.

To deal with voltage source inverter, this has a fixed dc bus voltage and is modulated using sine triangle PWM. It is modulated such that the inverters are in the overmodulation region; i.e., the peak of these sinusoidal wave voltages ishigher than the peak of the carrier.

So, we want the line to line voltages to be sinusoidal, one way of ensuring, but not necessarily the only way is to make sure that  $V_{R(AV)}$ ,  $V_{YO(AV)}$ , and  $V_{BO(AV)}$  are sinusoidal. Here we will restrict  $m_R$  to the peak value of modulating wave ( $V_P$ ) when operating in linear modulation region. In over-modulation  $m_R$  will go higher than  $V_P$ , but even if it goes higher than that, but pole voltage restricted to  $\pm \frac{Vdc}{2}(1 \text{ p.u.})$  exactly

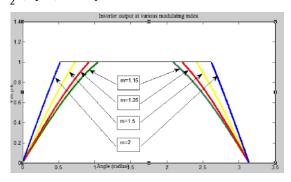

Fig.1: Inverter Output at Various Modulation Indexes

In Figure 1, we want to show that if the modulation index

Int. j. eng. bus. manag. www.aipublications.com is increased, then the waveform is flatter pulse dropping tendency also increases (explain later). So the switching tendency of each switch is reduced drastically. As a consequence, we can use very high frequency in the carrier. If the peak value of the carrier wave is lesser than the modulating wave, then this is clipped shown in figure 6, and it cannot exceed  $\frac{V_{dc}}{2}$ . Similarly, it will be clipped at the most negative average pole voltage that can be applied. The bottom device is continuously on, and therefore, thepole voltagewill be  $-\frac{V_{dc}}{2}$  (1p.u.) throughout the sub-cycle. In that case, the average pole voltage is  $-\frac{V_{dc}}{2}$ (-1p.u.), it cannot be more than that. In the same way, we can see that it is true about the Y and B phases.

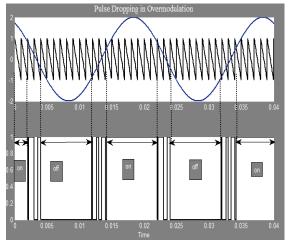

Fig.2: Pulse Dropping inOver-Modulation region

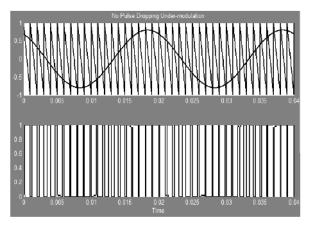

Fig.3: No-Pulse Dropping in Under Modulation Region

Here our depth of over-modulation depends on the modulation index. So, according to Figure 6,the double arrow is the region during which the R phase is not switching (i.e., pulse dropping). The top gate device will be continuously on. Similarly, on the next pulse dropping, it is continuously off here. So, there are no pulses at on and off region; that is why it is called pulse

### dropping.

By comparing Figures 2and Figure 3, we can quickly examine the pulse dropping nature of the same device with under and over-modulation.

# III. RESULTS

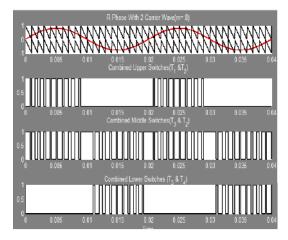

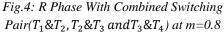

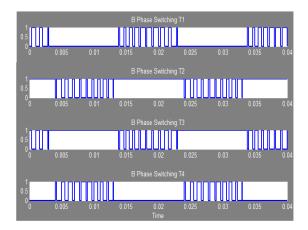

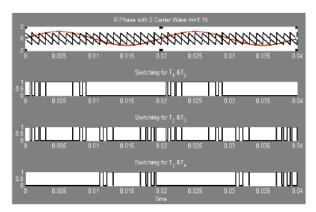

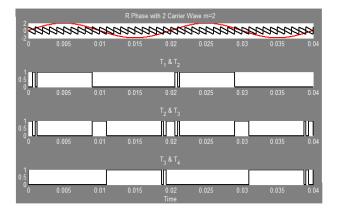

In this section, the switching pulse will be shown in over and under-modulation region. Under the modulating switching, pulses have been shown so that we can compare over-modulated switching pulses.In Figure 4 first window represents the carrier wave with 2 levels-shifted modulating waves. In the next 3 windows of the same figure, follow the previous window in these windows upper switches  $(T_1 \& T_2)$  will be closed if modulating wave is above both carrier waves. If modulating waves in between both carrier waves, then middle switches  $(T_2 \& T_3)$  will be closed. One thing keeps in mind  $T_2$  switches are closed in both situations. Similarly, lower switches  $T_3 \& T_4$  will be closed if the modulating waves are lesser than both carrier waves. In this case, the switch  $T_3$  is common.

The MATLAB simulation environment is used with the following POWERGUI setting.

Table1: POWERGUI Setting

| 1 | Solver                | ODE23tb(Stiff/TR/BDF2 |

|---|-----------------------|-----------------------|

| 2 | Discrete<br>step time | 50*10-6 Sec           |

| 3 | Simulation<br>Time    | 0.04 Sec              |

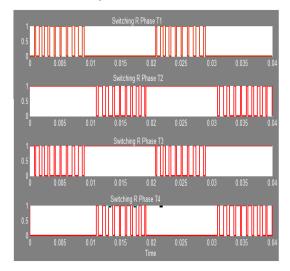

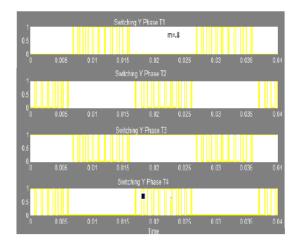

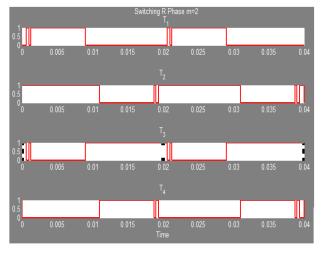

In Figure 5,the individual pulse of R phase switches is shown as we mention earlier, switches  $T_1 \& T_3$  and  $T_2 \& T_4$  are complimentary with each other. It has been

seen clearly. Similarly, Y and B phase switching pulses waveforms shown continuously in Figure 6 and Figure 7. In the next case at zone, I (m=1.15) pulse dropping is started, but it is very less.

Fig.5: Switching Pulses for R Phase Switches at m=0.8.

Fig.6: Switching Pulses for Y Phase Switches at m=0.8.

Fig.7: Switching Pulses for B Phase Switches at m=0.8.

Fig.8: R Phase With Combined Switching  $Pairs(T_1 \& T_2, T_2 \& T_3, and T_3 \& T_4)$  at m=1.15.

*Fig.9: .R Phase With Combined Switching Pairs*( $T_1 \& T_2, T_2 \& T_3$ , and  $T_3 \& T_4$ ) at m=2.0

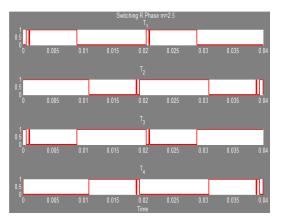

Fig.10: Switching Pulses for R Phase Switches at m=2.0

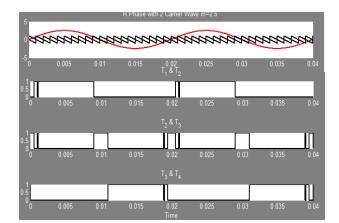

Fig.11: R Phase With Combined Switching Pairs $(T_1 \& T_2, T_2 \& T_3, and T_3 \& T_4)$  at m=2.5.

Fig.12.Switching Pulses for R Phase Switches at m=2.5.

After examining Figures 5,6 and 7 we can say that all phase figure are same except  $120^{0}$  phasor shifting. It is evident because the modulating waves also have  $120^{0}$  phase-shifting. To show the pulses dropping nature, we have to go to the depth of over-modulation (zone 1,2& 3) in various cases we have studied, and the tendency of pulse dropping will increase if we enter in higher modulating depth. If we enter high modulation indexes (zone III) (figures no 9-12), then switching operation approximately equal to 6 step operation is valid for 2 levels as well as for MLI also. In this case, the switching frequency is very less; however, the THD is very high. In this case, low harmonic frequency voltage and current are very high, and to compensate these ripples, we have to design the compensator.

# **IV. CONCLUSIONS**

Among the various reasons, one of the most important reasons is to increase the DC bus utilization. Now with sine triangle PWM the maximum fundamental voltage whatever we could get was (fundamental voltage $0.5V_{dc}$  after adding third harmonic injection we can get  $0.577V_{dc}$  i.e. 15% more) but in over-modulation, we can get maximum 6 step voltage i.e. $0.644V_{dc}$  of fundamental voltage. But there is a problem; it introduces low-frequency distortion in the output.

#### REFERENCES

- [1] Goyal, Sunil Kumar, et al. "Economic load dispatch with emission and line constraints using biogeography based optimization technique." 2020 International Conference on Intelligent Engineering and Management (ICIEM). IEEE, 2020..

- [2] Modi B, Lalwani M. The design and implementation of voltage stabiliser for nullifying temperature impact on PV array with grid-connected systems. International Journal of Renewable Energy Technology. 2022;13(2):144-77..

- [3] Modi B, Lalwani M. Designing and testing clipper-clamper based solar photovoltaic controller for mitigating partial shading effect. Applied Solar Energy. 2022 Aug;58(4):503-16.

- [4] Tandon, A., Nawaz, S., & Siddqui, S. A. (2020). Cost– Benefit Analysis in Distribution System of Jaipur City After DG and Capacitor Allocation. In Intelligent Computing Techniques for Smart Energy Systems: Proceedings of ICTSES 2018 (pp. 351-358). Springer Singapore.

- [5] Nawaz, Sarfaraz, Md Imran, and Sonali Singh. "A novel approach for multiple DG allocation in distribution system of jaipur city." In 2017 International Conference on Information, Communication, Instrumentation and Control (ICICIC), pp. 1-6. IEEE, 2017.

- [6] S. Jain and N. Kanwar, "Day ahead optimal scheduling of generators using Dynamic Programming method," 2019 8th International Conference on Power Systems (ICPS), Jaipur, India, 2019, pp. 1-6, doi: 10.1109/ICPS48983.2019.9067555.